この記事は ハードウェア開発、CPUアーキテクチャ Advent Calendar 2016 - Qiita の1日目の記事です。

Advent-Calendarを埋めてくれるかた、今からでも募集中です!是非参加してください!

僕一人では、クオリティのある記事を続けられそうにありません。。。(弱音)

という訳で、私は今年一年で急激に注目を浴び始めたRISC-Vについて、あらためて纏めていこうと思う。

﹁改めて﹂と書いてあるとおり、私が一番最初に紹介したRISC-Vの記事は以下なので、こっちも参照してね。

msyksphinz.hatenablog.com

この記事は ハードウェア開発、CPUアーキテクチャ Advent Calendar 2016 - Qiita の1日目の記事です。

Advent-Calendarを埋めてくれるかた、今からでも募集中です!是非参加してください!

僕一人では、クオリティのある記事を続けられそうにありません。。。(弱音)

という訳で、私は今年一年で急激に注目を浴び始めたRISC-Vについて、あらためて纏めていこうと思う。

﹁改めて﹂と書いてあるとおり、私が一番最初に紹介したRISC-Vの記事は以下なので、こっちも参照してね。

msyksphinz.hatenablog.com

RISC-Vの生い立ち

今でこそ随分と知名度を得たRISC-Vだがが、私が一番最初に発見した日本語の記事は、以下と記憶している。 keisanki.at.webry.info この記事を見て、﹁面白そう!﹂と思ったので、自分で調べながら記事を書き始めたのが最初。 さらに言うならば、2013年のHot-chipsにて以下のポスターセッションがあったようだ。 ●The RISC-V Instruction Set http://www.hotchips.org/wp-content/uploads/hc_archives/hc25/HC25-posters/HC25.26.p70-RISC-V-Warterman-UCB.pdf さらに、初期のRISC-Vの命令セットリファレンスマニュアルを見ていると、2011年という記述が出ており、ずいぶんと昔から検討されていたアーキテクチャなのだなということが分かる。 ●The RISC-V Instruction Set Manual Volume I: Base User-Level ISA https://people.eecs.berkeley.edu/~krste/papers/EECS-2011-62.pdfRISC-Vの目的

RISC-Vの目的とはいったい何なのだろうか? まずはRISC-VのISA仕様書を読んでみよう。Introductionに(仕様書とは思えないような)設計者の思いが書いてある。 We developed RISC-V to support our own needs in research and education, where our group is particularly interested in actual hardware implementations of research ideas (we have completed eleven different silicon fabrications of RISC-V since the first edition of this specification), and in providing real implementations for students to explore in classes (RISC-V processor RTL designs have been used in multiple undergraduate and graduate classes at Berkeley). まずは、RISC-Vの設計者とMIPSの設計者が同じ流れを組んでいることから分かる通り、過去の遺産を大量に抱えているMIPSアーキテクチャから決別した、新しいアーキテクチャが必要だったということだ。 プロセッサアーキテクチャを研究する人達は、自分の提案手法の効果を測定するためのリファレンスプロセッサモデルが必要だったのではないか?しかし、 ●リファレンスモデルとしてMIPSは過去の古い資産を含み過ぎている(遅延スロット、複雑な命令、複雑なレジスタ構成HI/LOなど) ●他のプロセッサアーキテクチャも、ライセンスなどの問題で自由に使えるものがあまり無い(ARMも大学の研究として使うのは難しく、またARM32のアーキテクチャはRISCと呼ぶにはあまりにも複雑だった。ARM64は知らない) ということから、誰もが自由に使用することができる、新しいデファクトスタンダードとしてのプロセッサアーキテクチャが必要だったという訳だ。最初は別に産業界に普及して欲しいとか、そういうことは考えていなかったのではなかろうか。RISC-Vの特徴

上記のとおり、RISC-Vは過去のMIPSという古いアーキテクチャの問題点を解決するように設計されている。最初の目的がMIPSの改善ということもあり、MIPSの問題点を解決すべく設計されているような印象だ。 ●遅延スロットは存在しない ●命令セットは単純 ●フラグは存在しない ●HI/LOレジスタは存在しない ●命令セットはより単純にアーキテクチャレベルについて

RISC-Vにはいくつかのアーキテクチャレベルが存在する。整数、浮動小数点のアーキテクチャセットの区別はもちろん(RV32I, RV32-Fみたいな)、64ビット整数命令、64ビット倍精度浮動小数点命令、さらには128ビット整数命令まで定義されている。 RISC-V Spec 2.1を改めて読み直すと、いろいろアーキテクチャレベルが追記されている。 Specifications - RISC-V Foundation| 名称 | 内容 | 備考 |

|---|---|---|

| RV32I | base integer instruction set | |

| RV32E | base integer instruction set, which is a reduced version of RV32I designed for embedded systems | |

| RV64I | base integer instruction set, which builds upon the RV32I. | |

| “M” Standard Extension | standard integer multiplication and division instruction extension | |

| “A” Standard Extension | standard atomic instruction extension. | |

| “F” Standard Extension | standard instruction-set extension for single-precision floating-point. | |

| “D” Standard Extension | standard double-precision floating-point instruction-set extension. | |

| “Q” Standard Extension | standard extension for 128-bit binary floating-point instructions. | |

| “L” Standard Extension | support decimal floating-point arithmetic | まだ詳細は定義されていないが。 |

| “C” Standard Extension | draft proposal for the RISC-V standard compressed instruction. | RV32Eよりもより小さくした命令セットかな。 |

| “V” Standard Extension | vector instructions. | まだ定義されていない。 |

| “B” Standard Extension | future standard extension to provide bit manipulation instructions | まだ定義されていない。 |

| “T” Standard Extension | transactional memory operations. | まだ定義されていない。 |

| “P” Standard Extension | standard packed-SIMD extension for RISC-V | 命令セットの空間だけは予約してある? |

| RV128I | variant of the RISC-V ISA supporting a flat 128-bit address space |

ちなみに、システムレベル命令(システムコールとか、割り込み)などは別の仕様書に定義されている。

Draft Privileged ISA Specification v1.10 - RISC-V Foundation

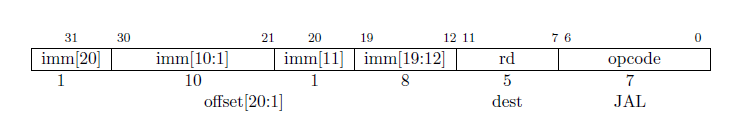

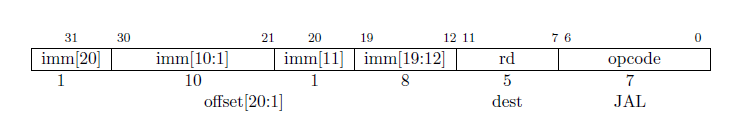

RISC-Vの即値生成は、他の命令の即値フィールドと合わせるためにこのようなビットフィールドになっている。これにより即値生成の回路を単純化するという目的がある。

RISC-Vの即値生成は、他の命令の即値フィールドと合わせるためにこのようなビットフィールドになっている。これにより即値生成の回路を単純化するという目的がある。

備考: OpenRISCじゃ駄目なのかい?

これもアーキテクチャ仕様書に言及がある。OpenRISCにはOpenRISCの問題点が残っている訳だ。 ●OpenRISC has condition codes and branch delay slots, which complicate higher performance implementations. ●OpenRISC uses a fixed 32-bit encoding and 16-bit immediates, which precludes a denser instruction encoding and limits space for later expansion of the ISA. ●OpenRISC does not support the 2008 revision to the IEEE 754 floating-point standard. ●The OpenRISC 64-bit design had not been completed when we began. 上記の資料を読めば分かるように、RISC-Vのアーキテクチャ仕様書を見て分かるとおり、命令エンコーディングについてはかなり工夫がされている。 最初にアーキ仕様書を読んだ人はびっくりするかもしれない。 RISC-Vの即値生成は、他の命令の即値フィールドと合わせるためにこのようなビットフィールドになっている。これにより即値生成の回路を単純化するという目的がある。

RISC-Vの即値生成は、他の命令の即値フィールドと合わせるためにこのようなビットフィールドになっている。これにより即値生成の回路を単純化するという目的がある。