| IBM Stretch | |

|---|---|

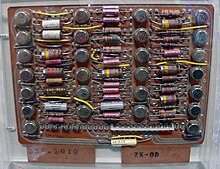

IBM 7030 maintenance console at the Musée des Arts et Métiers, Paris

| |

| Design | |

| Manufacturer | IBM |

| Designer | Gene Amdahl |

| Release date | May 1961 (May 1961) |

| Units sold | 9 |

| Price | US$7,780,000 (equivalent to $79,320,000 in 2023) |

| Casing | |

| Weight | 70,000 pounds (35 short tons; 32 t)[1] |

| Power | 100 kW[1] @ 110 V |

| System | |

| Operating system | MCP |

| CPU | 64-bit processor |

| Memory | 2048 kilobytes (262,144 x 64 bits)[1] |

| MIPS | 1.2 MIPS |

|

| |

The IBM 7030, also known as Stretch, was IBM's first transistorized supercomputer. It was the fastest computer in the world from 1961 until the first CDC 6600 became operational in 1964.[2][3]

Originally designed to meet a requirement formulated by Edward TelleratLawrence Livermore National Laboratory, the first example was delivered to Los Alamos National Laboratory in 1961, and a second customized version, the IBM 7950 Harvest, to the National Security Agency in 1962. The Stretch at the Atomic Weapons Research EstablishmentatAldermaston, England was heavily used by researchers there and at AERE Harwell, but only after the development of the S2 Fortran Compiler which was the first to add dynamic arrays, and which was later ported to the Ferranti AtlasofAtlas Computer Laboratory at Chilton.[4][5]

The 7030 was much slower than expected and failed to meet its aggressive performance goals. IBM was forced to drop its price from $13.5 million to only $7.78 million and withdrew the 7030 from sales to customers beyond those having already negotiated contracts. PC World magazine named Stretch one of the biggest project management failures in IT history.[6]

Within IBM, being eclipsed by the smaller Control Data Corporation seemed hard to accept.[7] The project lead, Stephen W. Dunwell,[8] was initially made a scapegoat for his role in the "failure",[9] but as the success of the IBM System/360 became obvious, he was given an official apology and, in 1966 was made an IBM Fellow.[10]

In spite of Stretch's failure to meet its own performance goals, it served as the basis for many of the design features of the successful IBM System/360, which was announced in 1964 and first shipped in 1965.

In early 1955, Dr. Edward Teller of the University of California Radiation Laboratory wanted a new scientific computing system for three-dimensional hydrodynamic calculations. Proposals were requested from IBM and UNIVAC for this new system, to be called Livermore Automatic Reaction CalculatororLARC. According to IBM executive Cuthbert Hurd, such a system would cost roughly $2.5 million and would run at one to two MIPS.[11]: 12 Delivery was to be two to three years after the contract was signed.

At IBM, a small team at Poughkeepsie including John Griffith and Gene Amdahl worked on the design proposal. Just after they finished and were about to present the proposal, Ralph Palmer stopped them and said, "It's a mistake."[11]: 12 The proposed design would have been built with either point-contact transistorsorsurface-barrier transistors, both likely to be soon outperformed by the then newly invented diffusion transistor.[11]: 12

IBM returned to Livermore and stated that they were withdrawing from the contract, and instead proposed a dramatically better system, "We are not going to build that machine for you; we want to build something better! We do not know precisely what it will take but we think it will be another million dollars and another year, and we do not know how fast it will run but we would like to shoot for ten million instructions per second."[11]: 13 Livermore was not impressed, and in May 1955 they announced that UNIVAC had won the LARC contract, now called the Livermore Automatic Research Computer. LARC would eventually be delivered in June 1960.[12]

In September 1955, fearing that Los Alamos National Laboratory might also order a LARC, IBM submitted a preliminary proposal for a high-performance binary computer based on the improved version of the design that Livermore had rejected, which they received with interest. In January 1956, Project Stretch was formally initiated. In November 1956, IBM won the contract with the aggressive performance goal of a "speed at least 100 times the IBM 704" (i.e. 4 MIPS). Delivery was slated for 1960.

During design, it proved necessary to reduce the clock speeds, making it clear that Stretch could not meet its aggressive performance goals, but estimates of performance ranged from 60 to 100 times the IBM 704. In 1960, the price of $13.5 million was set for the IBM 7030. In 1961, actual benchmarks indicated that the performance of the IBM 7030 was only about 30 times the IBM 704 (i.e. 1.2 MIPS), causing considerable embarrassment for IBM. In May 1961, Thomas J. Watson Jr. announced a price cut of all 7030s under negotiation to $7.78 million and immediate withdrawal of the product from further sales.

Its floating-point addition time is 1.38–1.50 microseconds, multiplication time is 2.48–2.70 microseconds, and division time is 9.00–9.90 microseconds.

While the IBM 7030 was not considered successful, it spawned many technologies incorporated in future machines that were highly successful. The Standard Modular System transistor logic was the basis for the IBM 7090 line of scientific computers, the IBM 7070 and 7080 business computers, the IBM 7040 and IBM 1400 lines, and the IBM 1620 small scientific computer; the 7030 used about 170,000 transistors. The IBM 7302 Model I Core Storage units were also used in the IBM 7090, IBM 7070 and IBM 7080. Multiprogramming, memory protection, generalized interrupts, the eight-bit byte for I/O[a] were all concepts later incorporated in the IBM System/360 line of computers as well as most later central processing units (CPU).

Stephen Dunwell, the project manager who became a scapegoat when Stretch failed commercially, pointed out soon after the phenomenally successful 1964 launch of System/360 that most of its core concepts were pioneered by Stretch.[13] By 1966 he had received an apology and been made an IBM Fellow, a high honor that carried with it resources and authority to pursue one's desired research.[13]

Instruction pipelining, prefetch and decoding, and memory interleaving were used in later supercomputer designs such as the IBM System/360 Models 91, 95 and 195, and the IBM 3090 series as well as computers from other manufacturers. As of 2021[update], these techniques are still used in most advanced microprocessors, starting with the 1990s generation that included the Intel Pentium and the Motorola/IBM PowerPC, as well as in many embedded microprocessors and microcontrollers from various manufacturers.

The 7030 CPU uses emitter-coupled logic (originally called current-steering logic)[14] on 18 types of Standard Modular System (SMS) cards. It uses 4,025 double cards (as shown) and 18,747 single cards, holding 169,100 transistors, requiring a total of 21 kW power.[15]: 54 It uses high-speed NPN and PNP germanium drift transistors, with cut-off frequency over 100 MHz, and using ~50 mW each.[15]: 57 Some third level circuits use a 3rd voltage level. Each logic level has a delay of about 20 ns. To gain speed in critical areas emitter-follower logic is used to reduce the delay to about 10 ns.[15]: 55

It uses the same core memory as the IBM 7090.[15]: 58

The Lawrence Livermore Laboratory's IBM 7030 (except for its core memory) and portions of the MITRE Corporation/Brigham Young University IBM 7030 now reside in the Computer History Museum collection, in Mountain View, California.

Instructions are either 32-bit or 64-bit.[18]

The registers overlay the first 32 addresses of memory as shown.[19]

| ! Address | Mnemonic | Register | Stored in: |

|---|---|---|---|

| 0 | $Z | 64-bit zero: always reads as zero, cannot be changed by writes | Main core storage |

| 1 | $IT | interval timer (bits 0..18): decremented at 1024 Hz, recycles about every 8.5 minutes, at zero it turns on the "time signal indicator" in the indicator register | Index core storage |

| $TC | 36-bit time clock (bits 28..63): count of 1024 Hz ticks, bits 38..63 increment once per second, recycles each ~777 days. | ||

| 2 | $IA | 18-bit interruption address | Main core storage |

| 3 | $UB | 18-bit upper boundary address (bits 0-17) | Transistor register |

| $LB | 18-bit lower boundary address (bits 32-49) | ||

| 1-bit boundary control (bit 57): determines whether addresses within or outside the boundary addresses are protected | |||

| 4 | 64-bit maintenance bits: only used for maintenance | Main core storage | |

| 5 | $CA | channel address (bits 12..18): readonly, set by the "exchange", an i/o processor | Transistor register |

| 6 | $CPUS | other CPU bits (bits 0..18): signaling mechanism for a cluster of up to 20 CPUs | Transistor register |

| 7 | $LZC | left zeroes count (bits 17..23): number of leading zero bits from a connective result or floating point operation | Transistor register |

| $AOC | all-ones count (bits 44..50): count of bits set in connective result or decimal multiple or divide | ||

| 8 | $L | Left half of 128-bit accumulator | Transistor register |

| 9 | $R | Right half of 128-bit accumulator | |

| 10 | $SB | accumulator sign byte (bits 0..7) | |

| 11 | $IND | indicator register (bits 0..19) | Transistor register |

| 12 | $MASK | 64-bit mask register: bits 0..19 always 1, bits 20..47 writable, bits 48..63 always 0 | Transistor register |

| 13 | $RM | 64-bit remainder register: set by integer and floating point divide instructions only | Main core storage |

| 14 | $FT | 64-bit factor register: changed only by the "load factor" instruction | Main core storage |

| 15 | $TR | 64-bit transit register | Main core storage |

| 16 ... 31 |

$X0 ... $X15 |

64-bit index registers (sixteen) | Index core storage |

The accumulator and index registers operate in sign-and-magnitude format.

Main memory is 16K to 256K 64-bit binary words, in banks of 16K.

The memory was immersion oil-heated/cooled to stabilize its operating characteristics.

| Records | ||

|---|---|---|

| Preceded by | World's most powerful computer 1961–1963 |

Succeeded by |

| Authority control databases: National |

|

|---|